# Lecture Notes in Computer Science Edited by G. Goos, J. Hartmanis and J. van Leeuwen

1863

Springer

# Languages and Compilers for Parallel Computing

12th International Workshop, LCPC'99 La Jolla, CA, USA, August 4-6, 1999 Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

#### Volume Editors

Larry Carter

Jeanne Ferrante

University of California, San Diego

Department of Computer Science

9500 Gilman Drive, La Jolla, CA 92093-0114, USA

E-mail: {carter, ferrante}@cs.ucsd.edu

Cataloging-in-Publication Data applied for

ISBN 3-540-67858-1

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Languages and compilers for parallel computing: 12th international workshop; proceedings / LCPC '99, La Jolla, CA, USA, August 4 - 6, 1999. Larry Carter; Jeanne Ferrante (ed.). - Berlin; Heidelberg; New York; Barcelona; Hong Kong; London; Milan; Paris; Singapore; Tokyo: Springer, 2000 (Lecture notes in computer science; Vol. 1863)

CR Subject Classification (1998): D.3, D.1.3, F.1.2, B.2.1, C.2

ISSN 0302-9743 ISBN 3-540-67858-1 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH © Springer-Verlag Berlin Heidelberg 2000 Printed in Germany

Typesetting: Camera-ready by author, data conversion by PTP-Berlin, Stefan Sossna Printed on acid-free paper SPIN: 10722248 06/3142 543210

#### **Preface**

In August 1999, the Twelfth Workshop on Languages and Compilers for Parallel Computing (LCPC) was hosted by the Hierarchical Tiling Research group from the Computer Science and Engineering Department at the University of California San Diego (UCSD). The workshop is an annual international forum for leading research groups to present their current research activities and the latest results. It has also been a place for researchers and practitioners to interact closely and exchange ideas about future directions. Among the topics of interest to the workshop are language features, code generation, debugging, optimization, communication and distributed shared memory libraries, distributed object systems, resource management systems, integration of compiler and runtime systems, irregular and dynamic applications, and performance evaluation. In 1999, the workshop was held at the International Relations/Paci c Studies Auditorium and the San Diego Supercomputer Center at UCSD. Seventy-seven researchers from Australia, England, France, Germany, Korea, Spain, and the United States attended the workshop, an increase of over 50% from 1998.

The program committee of LCPC D9 along with external reviewers as needed, were responsible for evaluating the submitted papers. Forty-eight papers were submitted, and of those, twenty-seven were selected to be presented as full papers at the workshop. In addition, thirteen submissions were presented as posters in a special poster session. Using feedback provided both before and after the presentations, all authors were given the opportunity to improve their papers before submitting the nal versions contained in this volume. Short abstracts of the poster presentations are also included.

In addition to the paper and poster sessions, LCPC D9 also featured an invited talk by Burton Smith, Chief Scientist at Tera Computer (now renamed Cray) on "Optimization for the Tera MTA". This talk gave an overview of the MTA architecture and the program transformations in the MTA compiler that allow it to take advantage of the MTAL unique architectural characteristics. The home of the rst Tera MTA is the San Diego Supercomputer Center, and a tour of SDSC, including the Tera MTA, was o ered to all participants. We gratefully thank Burton Smith for his excellent presentation and for his full participation in the workshop.

A nal feature of this years workshop was a panel session on Benchmarking organized by Keshav Pingali. This session grew out of a seminar on Tiling for Optimal Resource Allocation (hosted by the International Conference and Research Center for Computer Science at Schloss Dagstuhl in 1998) in which setting up a suite of benchmarks for locality that could be used by the general community was proposed. The panel, whose members also included Rudi Eigenmann, David Padua, and Sanjay Rajopadhye, presented a lively and diverse discussion on the merits of such a suite.

#### VI Preface

The organizers wish to acknowledge the San Diego Supercomputer Center and UCSD for their help. In particular, the conference was organized by Joann Pagan of UCSD Conference Services, with help from Nancy Jensen at SDSC. We especially wish to thank the software support sta , particularly Cindy Paloma, and graduate students Kang Su Gatlin, Karin Hogstedt, Beth Simon, and Michelle Mills Strout, all of the Computer Science and Engineering Department, for their excellent help. We also wish to acknowledge the great help of Chanathip Namprempre in editing and putting together this volume.

We would like to give special thanks to the LCPCD9 program committee and the nameless external reviewers for their e orts in reviewing the submissions. Both the steering committee and the program committee helped with advice and suggestions on the organization of the workshop. Finally, we wish to thank all of the participants who helped to create a lively and constructive atmosphere of discussion, and the authors for sharing their signi cant research with us at LCPC D9.

May 2000

Larry Carter, Jeanne Ferrante Program Chair LCPCD9

### Organization

#### **Program Committee**

Program Chair: Larry Carter (University of California, San Diego, USA)

Jeanne Ferrante (University of California, San Diego, USA)

General Chair: Larry Carter (University of California, San Diego, USA)

Jeanne Ferrante (University of California, San Diego, USA)

Program Committee: Larry Carter (University of California, San Diego, USA)

Jeanne Ferrante (University of California, San Diego, USA)

Manish Gupta (IBM Research, USA) Zhiyuan Li (Purdue University, USA) Sam Midki (IBM Research, USA) Jose Moreira (IBM Research, USA)

Jan Prins (University of North Carolina at Chapel Hill, USA)

Pen-Chung Yew (University Minnesota, USA)

#### Panel

Keshav Pingali (Cornell University, USA) (organizer) Rudi Eigenmann (Purdue University, USA) David Padua (University of Illinois at Urbana Champaign, USA) Sanjay Rajopadhy (IRISA, France)

#### Steering Committee

Utpal Banerjee (Intel Corporation, USA)

Alex Nicolau (University of California, Irvine, USA)

David Gelernter (Yale University, USA)

David Padua (University of Illinois at Urbana Champaign, USA)

#### **Sponsoring Institutions**

San Diego Supercomputer Center, La Jolla, CA USA University of California, San Diego, La Jolla, CA USA

# **Table of Contents**

| Java                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| High Performance Numerical Computing in Java: Language and Compiler Issues                                                              |

| Pedro V. Artigas, Manish Gupta, Samuel P. Midkiff, and<br>José E. Moreira                                                               |

| Instruction Scheduling in the Presence of Java's Runtime Exceptions 18  Matthew Arnold, Michael Hsiao, Ulrich Kremer, and Barbara Ryder |

| Dependence Analysis for Java                                                                                                            |

| Low-Level Transformations A                                                                                                             |

| Comprehensive Redundant Load Elimination for the IA-64 Architecture $\dots$ 55 Youngfeng Wu and Yong-fong Lee                           |

| Minimum Register Instruction Scheduling: A New Approach for Dynamic Instruction Issue Processors                                        |

| Unroll-Based Copy Elimination for Enhanced Pipeline Scheduling 85 Suhyun Kim, Soo-Mook Moon, Jinpyo Park, and HanSaem Yun               |

| Data Distribution                                                                                                                       |

| A Linear Algebra Formulation for Optimising Replication in Data Parallel                                                                |

| Programs                                                                                                                                |

| Accurate Data and Context Management in Message-Passing Programs 117  Dhruva R. Chakrabarti and Prithviraj Banerjee                     |

| An Automatic Iteration/Data Distribution Method Based on Access  Descriptors for DSMM                                                   |

| High-Level Transformations                                                                                                              |

| Inter-array Data Regrouping                                                                                                             |

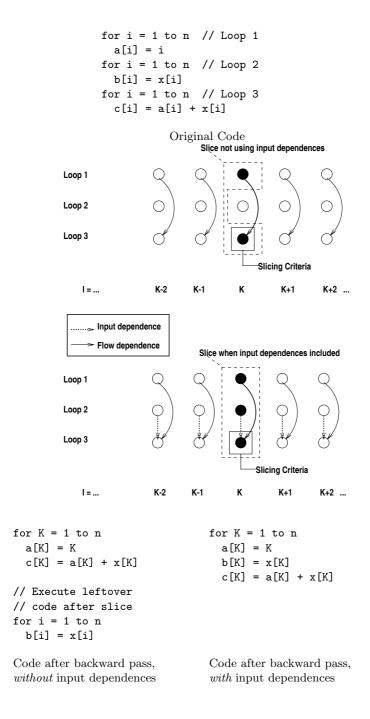

| Iteration Space Slicing for Locality                                                                   |

|--------------------------------------------------------------------------------------------------------|

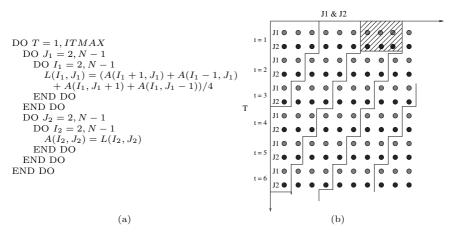

| A Compiler Framework for Tiling Imperfectly-Nested Loops                                               |

| Models                                                                                                 |

| Parallel Programming with Interacting Processes                                                        |

| Application of the Polytope Model to Functional Programs                                               |

| Multilingual Debugging Support for Data-Driven and Thread-Based Parallel Languages                     |

| Array Analysis                                                                                         |

| An Analytical Comparison of the I-Test and Omega Test                                                  |

| The Access Region Test                                                                                 |

| A Precise Fixpoint Reaching Definition Analysis for Arrays                                             |

| Demand-Driven Interprocedural Array Property Analysis                                                  |

| Language Support                                                                                       |

| Language Support for Pipelining Wavefront Computations                                                 |

| The Data Mover: A Machine-Independent Abstraction for Managing Customized Data Motion                  |

| Optimization of Memory Usage Requirement for a Class of Loops Implementing Multi-dimensional Integrals |

| Compiler Design and Cost Analysis                                                                      |

| Compile-Time Based Performance Prediction                                                              |

| Designing the Agassiz Compiler for Concurrent Multithreaded                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architectures                                                                                                                                                                                 |

| The Scc Compiler: SWARing at MMX and 3DNow!                                                                                                                                                   |

| Low-Level Transformation B                                                                                                                                                                    |

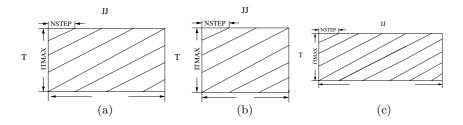

| Loop Shifting for Loop Compaction                                                                                                                                                             |

| Speculative Predication Across Arbitrary Interprocedural Control Flow 432 ${\it Hank~G.~Dietz}$                                                                                               |

| Posters                                                                                                                                                                                       |

| Porting an Ocean Code to MPI Using TSF                                                                                                                                                        |

| A Geometric Semantics for Program Representation in the Polytope Model 451 $Brian\ J.\ d'Auriol$                                                                                              |

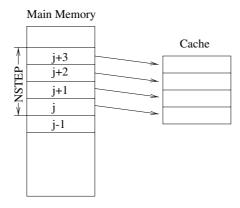

| Compiler and Run-Time Support for Improving Locality in Scientific Codes                                                                                                                      |

| Code Restructuring for Improving Real Time Response through<br>Code Speed, Size Trade-offs on Limited Memory Embedded DSPs 459<br>Vipin Jain, Siddharth Rele, Santosh Pande, and J. Ramanujam |

| Compiling for Speculative Architectures                                                                                                                                                       |

| Symbolic Analysis in the PROMIS Compiler                                                                                                                                                      |

| Data I/O Minimization for Loops on Limited Onchip Memory Processors . 472 $Lei\ Wang\ and\ Santosh\ Pande$                                                                                    |

| Time Skewing for Parallel Computers                                                                                                                                                           |

| Run-Time Parallelization Optimization Techniques                                                                                                                                              |

| Thresholding for Work Distribution of Recursive, Multithreaded Functions 485  Gary M. Zonnetti, Gagan Agrawal, and Lori L. Pollock                                                            |

#### XII Table of Contents

| An Empirical Study of Function Pointers Using SPEC Benchmarks 490 |

|-------------------------------------------------------------------|

| Ben-Chung Cheng and Wen-mei W. Hwu                                |

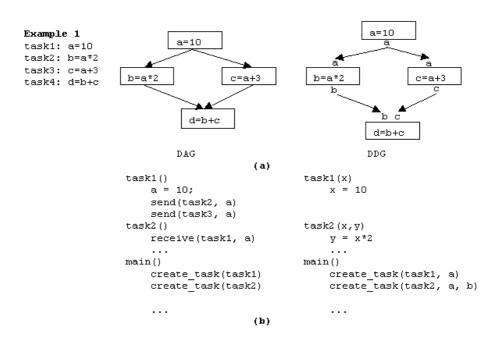

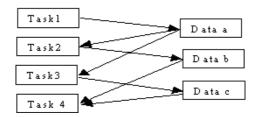

| Data Driven Graph: A Parallel Program Model for Scheduling        |

| Author Index                                                      |

# High Performance Numerical Computing in Java: Language and Compiler Issues

Pedro V. Artigas, Manish Gupta, Samuel P. Midkiff, and José E. Moreira

IBM Thomas J. Watson Research Center Yorktown Heights NY 10598-0218 {artigas,mgupta,smidkiff,jmoreira}@us.ibm.com

**Abstract.** Poor performance on numerical codes has slowed the adoption of Java within the technical computing community. In this paper we describe a prototype array library and a research prototype compiler that support standard Java and deliver near-Fortran performance on numerically intensive codes. We discuss in detail our implementation of: (i) an efficient Java package for true multidimensional arrays; (ii) compiler techniques to generate efficient access to these arrays; and (iii) compiler optimizations that create safe, exception free regions of code that can be aggressively optimized. These techniques work together synergistically to make Java an efficient language for technical computing. In a set of four benchmarks, we achieve between 50 and 90% of the performance of highly optimized Fortran code. This represents a several-fold improvement compared to what can be achieved by the next best Java environment.

#### 1 Introduction

Despite the advantages of Java<sup>(TM)1</sup> as a simple, object oriented programming language, it has not been widely adopted within the technical computing community. The primary reason for this is that the performance of technical computing programs written in Java, and executed with currently available commercial Java environments, trails far behind the equivalent Fortran programs. In this paper we discuss a prototype array library and a prototype research compiler developed by the Numerically Intensive Java group at IBM Research that allows standard Java programs to achieve Fortran-like performance. These techniques deliver several-fold speedups on uniprocessor codes. They make Java a practical language for numerical computing.

There are several Java language features which together degrade Java performance in the domain of technical computing. Three very useful Java features – (i) array reference and null-pointer checks; (ii) using objects to represent all but the most widely used numeric types; and (iii) the structure of Java arrays – are extremely detrimental to performance in the domain of numerical computing [1]. Most compiler research on Java has focused on optimizations for more general applications, leading to naive (from the point of view of technical computing) implementations of the features mentioned above. These naive implementations lead to poor performance, reinforcing the perception that Java is not appropriate for technical computing and reducing the emphasis on improving Java performance for numerical applications.

<sup>&</sup>lt;sup>1</sup> Java is a trademark of Sun Microsystems Inc.

L. Carter and J. Ferrante (Eds.): LCPC'99, LNCS 1863, pp. 1-17, 2000.

We will now give an overview of the detrimental effects of these language features. The rest of the paper will discuss in detail our library and compiler approach and how it overcomes these detrimental effects. Our approach is an example of language and compiler codesign. Although we make absolutely no modifications to the Java language per se, we introduce a class library (a package) for multidimensional arrays and advocate its use in developing technical codes. (An implementation of the Array package can be downloaded for free from http://www.alphaworks.ibm.com. More information on our research can be found at http://www.research.ibm.com/ninja.) In effect, we grow the language without having to modify any part of it. The Array package has been designed to enable powerful compiler optimization techniques that significantly improve the performance of technical computing.

Array references and null-pointer checks: The Java language specification requires that references through a pointer first check that the pointer is not null. Java also requires that each array access be checked to ensure that the element being referenced is within the declared bounds of the array. Both features help enforce security and reliability of Java programs. On many architectures, the direct cost of the checks is quite low for valid references. The real problem arises from the combined effects of the required checks and Java's precise exception model [22]. Because Java strictly specifies the order of evaluation of expressions – including accesses of expression operands – an exception must appear to have been thrown exactly after previous accesses and operations have been performed in strict program order. This prohibits the reordering of accesses and operations that are the foundation of the aggressive optimizations that make Fortran a high performance language [27]. Our general solution is to create different static instances of the loop body, with and without bounds and null-pointer exceptions. The proper static instance is dynamically selected to execute the iteration space of the loop. The static instance of the loop body which has no exceptions can be aggressively optimized.

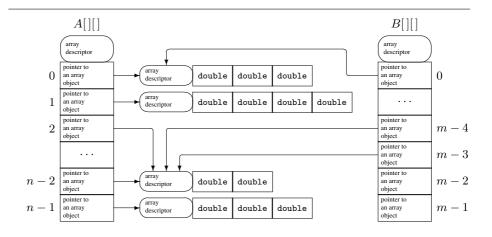

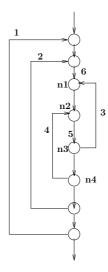

Efficient array structures: Java native arrays (which will be referred to as Java arrays, with a lower case first a) allow the construction of very general random access data structures. Unfortunately, this same generality makes the the array reference checking optimizations described above more expensive, and dataflow analysis necessary for aggressive optimization nearly impossible. Consider the example in Figure 1, which illustrates several problems with Java arrays. First, general optimization of bounds checking requires finding out the extent of all rows of a Java two-dimensional array. This is an O(n) operation, where n is the number of rows. If the array was known to be rectangular, it would be an O(1) operation. Second, different rows of the array can be aliased (e.g., rows 2 and n-2 of A) even though their indices have different values. This is an example of intra-array aliasing. It is also possible to have inter-array aliasing as shown in Figure 1 for rows 0 of B and A. Thus, pointer alias analysis, not the cheaper dependence analysis, is necessary for optimization. Because of the dynamic nature of Java arrays, the alias analysis is very difficult. Our solution to the problem with Java arrays is the creation of an Array package for Java. This Array package implements multidimensional rectangular Arrays (with a capital first A) which are necessary for technical computing. The Array package, combined with appropriate compiler optimizations, overcomes both the dataflow analysis problems and the array reference bounds checking problems.

Fig. 1. Structure of two-dimensional Java arrays.

The Array package for Java and its associate compiler optimizations create an environment that delivers both the functionality and performance of Fortran 90 programming in Java. (This approach is similar to other successful object-oriented numerical computing environments such as POOMA and A++/P++ [25,23,29].) We show in this paper that we can raise the performance of 100% pure Java from a mere 1-2% to 65-90% of highly optimized Fortran. Even when compared to the highest performing Java environment (JDK 1.1.8 with the IBM JIT) currently available for our platform, which already incorporates advanced optimizations such as bounds checking elimination, we still show a several-fold improvement in performance. We note that the Fortran codes we compare Java against are representative of truly optimized computations, that achieve between 35-90% of the hardware peak performance.

The rest of this paper is organized as follows. Section 2 describes our Array package for Java, discussing its main components and presenting an example of its usage. Section 3 describes the compiler optimizations that we implemented in conjunction with the Array package. Section 4 reports our experimental results from using the Array package with four numerical benchmarks. Finally, Section 5 discusses related work and Section 6 presents our conclusions.

#### 2 The Array Package for Java

A major design goal for the Array package was to overcome the limitations inherent in Java arrays in terms of performance and ease of use, without losing any key benefits of Java arrays or requiring any changes to the language semantics. The Array package provides the following benefits:

more expressivity: the package allows programmers to use high-level Array operations (like Array addition, transpose), which are similar to those provided by languages like Fortran 90.

- high performance: many design features allow programs using the Array package to achieve high performance: (i) the high-level array operations are written in a transactional style, discussed below, that enables aggressive compiler optimizations in spite of various exception checks; (ii) a high-performance BLAS (Basic Linear Algebra Subprograms) library is available as part of the Array package for common linear algebraic computations; and (iii) the basic Array access operations are amenable to efficient implementation and accurate compiler analysis.

- safety and security features of Java preserved: the requirements, mandated by Java semantics, for bounds checking and null-pointer checking are preserved; in fact, the Array package requires extensive checks for other exceptional conditions, like nonconforming Arrays for high-level Array operations, that arise in the context of the operations introduced in the package.

- flexibility of data layout: the actual data layout for the Arrays is not exposed to the programmer (as it is not specified). While this may prevent the programmer from doing certain optimizations, we believe this is beneficial in the longer term because it facilitates data layout optimizations for Arrays [9,16,18,19,26]. The compiler has fewer constraints on ensuring the correctness of the program in the presence of data layout transformations, and can avoid copy operations otherwise needed to restore the data layout to a fixed format.

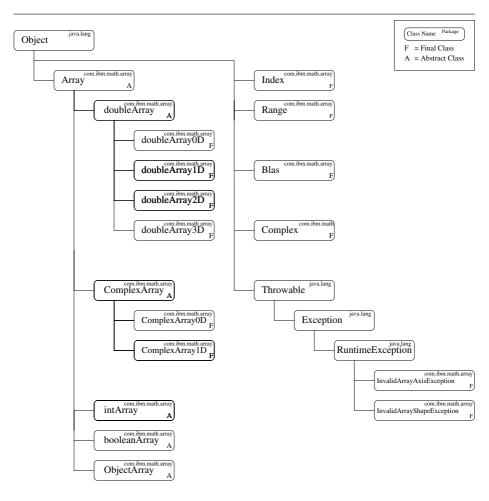

The class hierarchy of the Array package is shown in Figure 2. It has been defined to enable aggressive compiler optimizations. There is a separate class for each Array *elemental data type* and *rank* (currently, we support ranks 0 through 3). There are also separate classes for Arrays of complex numbers and Arrays of Objects. This approach enables easy static type checking of Arrays defined by the Array package. We make extensive use of *final* classes, since most Java compilers (and, in particular, *javac*) are able to apply method inlining to methods of final classes. Since the type and rank of an Array are defined by a final class, the semantics of any Array operation (and in particular element access) are defined statically. This is a key feature exploited in our optimization techniques. Obviously, by making the Array classes final we prevent application programmers from extending those classes directly. A *decorator* design pattern [13] can be used if programmers want to "extend" Array classes.

In contrast to Java arrays discussed in the previous section, an Array defined by the Array package has a nonragged rectangular shape and constant bounds over its lifetime. An axis of this Array can be indexed by either an integer (specifying a single element), a Range (specifying a triplet), or an Index (specifying an enumerated list). Indexing operations are used in *accessor methods* that read/write data from/to an Array, and in *sectioning methods* that create views of an Array. A valid index for an Array axis must be greater than or equal to zero and less than the extent of that axis.

All operations (methods and constructors) of the Array package have, in the absence of JVM failure, transactional behavior. That is, there are only two possible outcomes of an Array operation: (i) the operation completes without an exception being thrown, or (ii) an exception is thrown before any data is changed. This allows aggressive program transformations in the main computational part of the method, while honoring the Java exception semantics.

Fig. 2. Simplified class hierarchy chart.

#### 2.1 Package Methods

The Array package defines the following groups of methods:

- Array operations: These are scalar operations applied element-wise to a whole Array. The methods in this category include assignment, arithmetic and arithmetic-assign operations (analogous, for example, to += and \*= operators in Java), comparison operations, and logic operations (where appropriate for the elemental data type). These operations implement array semantics: In evaluating an expression (e.g., A += C), all data is first fetched (i.e., A and C are read from memory), the computation is performed (i.e., A + C is evaluated), and only then the result is stored (i.e., A is modified). The Array package uses a form of dynamic dependence analysis [3] to

determine when to use a temporary array to hold intermediate data and when it is safe to avoid using temporaries.

- Array manipulation: Methods in this group include section, permuteAxes and reshape. These methods operate on the Array as a whole, creating a new view of the data and returning a new Array object expressing this view. This new Array object shares its data with the old object when possible to avoid the overhead of data copying.

- Array accessor methods: The methods of this group include get and set operations. The get and set are basic accessor methods which use the indexing schemes described earlier. They can operate on individual elements as well as on regular and irregular sections of an Array.

- Array inquiry methods: Methods in this group include last, size, rank and shape.

They are fast, descriptor-only operations which return information about the (invariant) properties of an Array.

- BLAS routines: We have designed a BLAS [11] class as part of the Array package, to provide basic linear algebra functions for the multidimensional Arrays in that package. Note that this is a 100% Java implementation of BLAS, and not an interface to already existing native libraries.

#### 2.2 An Example

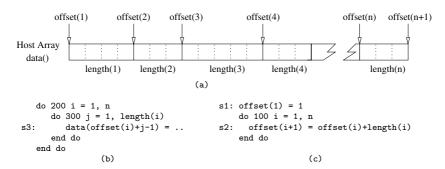

Figure 3 illustrates several features of the Array package by comparing two straightforward implementations of the basic BLAS operation dgemm. The dgemm operation computes  $C = \alpha A^* \times B^* + \beta C$ , where A, B, and C are matrices and  $\alpha$  and  $\beta$  are scalars.  $A^*$  can be either A or  $A^T$ . The same holds for  $B^*$ . In Figure 3(a) the matrices are represented as doubleArray2D objects from the Array package. In Figure 3(b) the matrices are represented as double[][].

The first difference is apparent in the interfaces of the two versions. The dgemm version for the Array package transparently handles operations on sections of a matrix. Section are extracted by the caller and passed on to dgemm as doubleArray2D objects. Section descriptors have to be explicitly passed to the Java arrays version, using the m, n, p, i0, j0, and k0 parameters.

Next, we note that the computational code in the Array package version is independent of the orientation of A or B. We just perform a (very cheap) transposition if necessary, by creating a new descriptor for the data using the permuteAxes method. In comparison, the code in the Java arrays version has to be specialized for each combination of orientation of A and B. (We only show the two cases in which A is not transposed.)

Finally, in the Array package version we can easily perform some shape consistency verifications before entering the computational loop. If we pass that verification, we know we will execute the entire loop iteration space without exceptions. Such verifications would be more expensive for the Java arrays, as we would have to traverse each row of the array to make sure they are all of the appropriate length. Furthermore, at least the row-pointer part of each array would have to be privatized inside the method, to guarantee that no other thread changes the shape of the array [22].

```

public static void dgemm(int transa,

int transb,

int m,

public static void dgemm(int transa,

int n,

int transb.

int p,

double alpha,

int i0, j0, k0,

doubleArray2D a,

double alpha,

doubleArray2D b,

double[][] a,

double beta,

double[][] b,

doubleArray2D c)

double beta,

throws NonconformingArrayException {

double[][] c) {

if (transa == Transpose)

if (transa != Transpose) {

a = a.permuteAxes(1,0);

if (transb != Transpose) {

if (transb == Transpose)

for (int i=i0; i<i0+m; i++) {

b = b.permuteAxes(1,0);

for (int j=j0; j<j0+p; j++) {

double s = 0;

int m = a.size(0);

for (int k=k0; k< k0+n; k++) {

int n = a.size(1);

s += a[i][k]*b[k][j];

int p = b.size(1);

c[i][j] = alpha*s+beta*c[i][j];

if (n != b.size(0))

throw new NonconformingArrayException();

}

if (p != c.size(1))

} else {

throw new NonconformingArrayException();

for (int i=i0; i<i0+m; i++) {

if (m != c.size(0))

for (int j=j0; j<j0+p; j++) {

throw new NonconformingArrayException();

double s = 0;

for (int k=k0: k<k0+n: k++) {

for (int i=0; i<m; i++) {

s += a[i][k]*b[j][k];

for (int j=0; j<p; j++) {

}

double s = 0;

c[i][j] = alpha*s+beta*c[i][j];

for (int k=0; k<n; k++) {

s += a.get(i,k)*b.get(k,j);

}

}

c.set(i,j,alpha*s+beta*c.get(i,j));

} else {

}

}

(a)

(b)

```

Fig. 3. An implementation of dgemm using (a) the Array package and (b) Java arrays.

#### 3 Compiler Optimizations

In this section we discuss the compiler support required to extract high performance of numerically intensive Java code written with the Array package. First we present an overview of our compiler infrastructure. Then we discuss the two major compiler optimizations that we implemented: semantic expansion [30] and bounds checking optimization [20].

#### 3.1 The IBM XL Family of Compilers

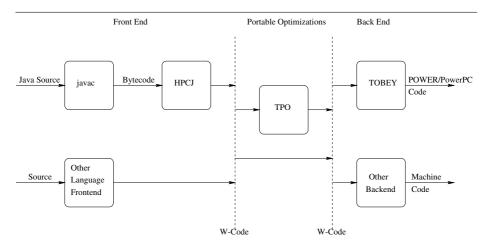

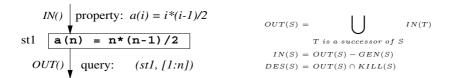

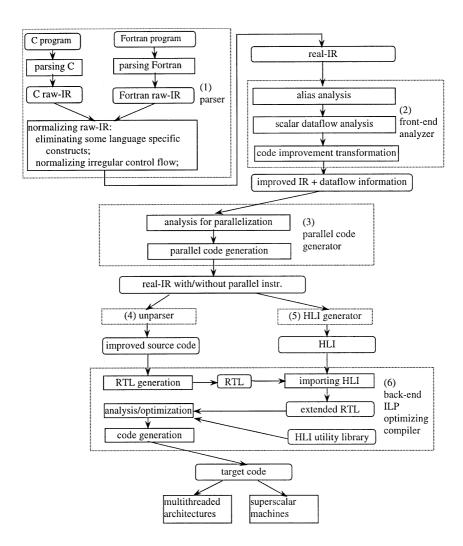

Our compiler infrastructure is based on the IBM XL family of compilers. Figure 4 shows the high-level architecture of these compilers. The compilers from the XL family are able to compile source code from various source languages and generate code for various target architectures. The compilation process consists of three major steps:

- 1. The language-specific front-end translates the source code into an intermediate representation called W-Code. For Java, this step is implemented by a combination of *javac*, which translates Java into bytecode, and the High Performance Compiler for Java (HPCJ), which translates bytecode into W-Code.

- 2. The portable optimizer implements language and architecture independent optimizations. It consumes and produces intermediate representations in W-Code. The portable optimizer step is implemented by TPO (Toronto Portable Optimizer).

- 3. The back-end implements architecture and implementation specific optimizations and generates the actual executable code. It translates W-Code to machine code. In our case, the back-end step is implemented by TOBEY, which generates executable code for the POWER and PowerPC families.

Our optimizations were implemented in two of the modules described above. Semantic expansion was implemented in HPCJ, because it is a language-dependent optimization. The bounds checking optimization was implemented in TPO because it is, in principle, independent of language and architecture (even though it is particularly useful for Java). We note that semantic expansion must, in any case, precede the bounds checking optimization to allow effective analysis of code using the Array package, which is necessary for applying bounds checking optimization on that code.

Fig. 4. Architecture of the XL family of compilers.

#### 3.2 Semantic Expansion of Array References

To avoid changing the Java language itself, we added support for true multidimensional arrays in the form of a set of classes comprising the Array package. All data access in the Array package is through accessor methods. In the absence of aggressive compiler optimizations, these method invocations are expensive, both in terms of their overhead

and in making analysis for the containing program regions very conservative. In order to obtain high performance, we must perform the array accesses in a more transparent, compiler-optimizable, way. We use the semantic expansion technique [30] to achieve this.

Our Java front-end (HPCJ) implements semantic expansion of the get and set accessor methods for Arrays. A call to a get or set method that accesses a single array element is replaced by inline code that performs the same array access, including the checks for null-pointer exception and out-of-bounds array exception that might be thrown due to that access. The compiler exploits information about the dense layout of Array data to generate code using the multidimensional array indexing operations in the W-Code intermediate representation. We note that this information could not have been exposed to the later compilation phases by applying regular method inlining instead of semantic expansion, since there is no Java bytecode for expressing references to true multidimensional arrays. The resulting code can be optimized by the W-Code based optimizer (TPO) using standard techniques (in conjunction with the bounds checking optimization). Thus, the Java Array package, combined with semantic expansion in the compiler, effectively provides the advantages of true multidimensional arrays in Java without any changes to the JVM or to the language itself and without violating the safety benefits provided by the Java language.

#### 3.3 Bounds Checking Optimization

The Java requirement that every array access be checked for null-pointer and out-of-bounds exceptions, coupled with its precise exceptions model, provides the benefits of safety and security, and also helps in the debugging of programs. On the other hand, it has a severe impact on the performance of numerical codes. The goal of the bounds checking optimization is to enable the generation of high performance machine code without eliminating the benefits provided by the exception checks (we use the term bounds checking loosely to cover null-pointer checks as well).

Our approach is to create *safe regions* by program transformation so that all array accesses in the safe regions are guaranteed not to generate a null-pointer or out-of-bounds exception [22]. This has both direct and indirect benefits. First, the exception checks on all array references inside the safe regions can be removed, reducing their direct overhead. Second, the safe region code can now be freely transformed (for example, using loop transformations like tiling) without violating the precise exceptions model of Java. In this work, we use the *versioning* technique to create safe and unsafe regions, with a run-time test to check whether the safe or the unsafe region should be executed [22]. The optimization is done in two phases: the *array range analysis phase* and the *safe region creation phase*. We note that this optimization can be applied to arrays in any language (including the Arrays from the Array package).

Array range analysis: In the analysis phase, the compiler obtains summary access information for each array with respect to the *intervals* (*i.e.*, the loops and the overall procedure) in a method. This information is represented using a bounded *regular section* descriptor (RSD) [7,17], which provides information about the lower bound and the upper bound on (read and write) accesses in each array axis. The procedure for computing

the bounded RSDs uses a combination of standard array analysis techniques and sophisticated symbolic analysis, described further in [15]. However, an important difference in the context of applying this analysis for the bounds checking optimization is that we can ignore certain aliasing information while identifying the section of an array that is read or written. For example, in Figure 5, we can summarize the access information for the array A accurately (for the purpose of the bounds checking optimization), even if A may potentially overlap any part of the array C. The bounds checks for A can be safely eliminated based only on the summary of accesses for A. Of course, a different transformation, such as loop reordering or parallelization, would have to consider the aliasing between A and C.

For cases where the compiler is unable to obtain, even symbolically, information about the range of array accesses, the corresponding range information is set to  $\bot$ , indicating an unknown value. For example, if the base address of an array A changes inside a loop in an unknown manner, the lower and upper bounds information for each axis of A is set to  $\bot$ .

Safe region creation: In this phase, the information from array range analysis is used to drive the versioning transformation which creates safe and unsafe regions. Our current implementation processes all loops in the method, and then selects each outermost loop for which complete array range information is symbolically available for every array reference (i.e., there are no ⊥ expressions in the array range information, although there may be symbolic variables appearing in the expressions which are invariant with respect to that loop). A duplicate code copy is created for each selected loop. From the copy which is to be made the safe region, all null-pointer checks and out-of-bounds checks for the arrays are eliminated. An expression for the run-time test, to check whether the safe or the unsafe region should be executed, is created in two parts: The first part verifies that none of the arrays is null. The second part verifies for each axis of every array that the lower and upper bounds of accesses are within the actual bounds of the array. This expression is simplified by expression-folding techniques.

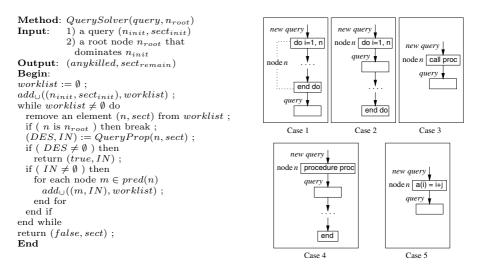

An example of Array range analysis and safe region creation: As an example of our bounds checking optimization technique, Figure 5 shows what happens with a simple code for matrix multiplication. For the purpose of clarity in this example, we use the notation A[i,j] to represent either A.get(i,j) or A.set(i,j,x). The original code, provided as input to the compiler, is shown in Figure 5(a). The CHK<sub>b</sub>() operation denotes explicit bounds checks for each index, while CHK<sub>n</sub>() denote the null-pointer checks. The code optimized through versioning is shown in Figure 5(b). The safe region contains no explicit checks and can be aggressively optimized.

The original code in Figure 5(a) contains three potential safe regions, one for each loop. For the innermost (k) region/loop we can prove that the range of accesses for the three Arrays are:

$$C[i:i,j:j]$$

$A[i:i,0:n-1]$

$B[0:n-1,j:j]$  (1)

```

if (A!=null)&&(B!=null)&&(C!=null)&&

(m-1 < A.size(0)) && (n-1 < A.size(1)) &&

(n-1 < B.size(0))\&\&(p-1 < B.size(1))\&\&

(m-1 < C.size(0)) \&\&(p-1 < C.size(1))  {

for (i=0; i \le m; i++)

for (j=0; j< p; j++)

for (i=0;i<m;i++)

for (k=0; k< n; k++)

for (j=0; j< p; j++)

C[i,j] = C[i,j] + A[i,k]*B[k,j];

for (k=0; k< n; k++)

CHK_n(C)[CHK_b(i),CHK_b(j)] =

} else {

CHK_n(C)[CHK_b(i),CHK_b(j)] +

for (i=0;i<m;i++)

\mathrm{CHK}_n(\mathtt{A})[\mathrm{CHK}_b(\mathtt{i}),\mathrm{CHK}_b(\mathtt{k})] *

CHK_n(B)[CHK_b(k),CHK_b(j)];

for (j=0; j< p; j++)

for (k=0; k< n; k++)

CHK_n(C)[CHK_b(i),CHK_b(j)] =

CHK_n(C)[CHK_b(i),CHK_b(j)] +

CHK_n(A)[CHK_b(i),CHK_b(k)] *

CHK_n(B)[CHK_b(k),CHK_b(j)];

}

(b)

(a)

```

**Fig. 5.** An example of safe region creation through range analysis and versioning: (a) the original code, (b) optimized code.

For the middle (j) loop we compute the following range information:

$$C[i:i,0:p-1]$$

$A[i:i,0:n-1]$

$B[0:n-1,0:p-1]$  (2)

And finally, for the outermost (i) loop we compute:

$$C[0:m-1,0:p-1]$$

$A[0:m-1,0:n-1]$

$B[0:n-1,0:p-1]$  (3)

Since complete information is available for the outermost loop, the compiler generates the versioning code of Figure 5(b). Note that the tests to verify in-bounds access with respect to the lower bounds of the arrays are folded away, as they evaluate to *true* at compile time.

#### 3.4 Array Package Advantages for Bounds Checking Optimization

We now discuss the advantages of using Arrays from the Array package over Java arrays, in terms of the complexity of the bounds checking optimization. First, since Java multi-dimensional Arrays are actually arrays of arrays, eliminating bounds checks completely on those arrays requires a limited form of pointer chasing analysis, to correlate references to different rows of the same base multidimensional array, while summarizing accesses to that array. Alternatively, an implementation could view two different rows of a multidimensional array as separate arrays, in which case, the optimization would only be effective for the last axis of the array. Second, in a multithreaded environment, we

need an array privatization scheme to prevent other threads from asynchronously changing the shape of the multidimensional array being subjected to the optimization [22]. For an  $(n_1 \times n_2 \times \ldots \times n_d)$  d-dimensional array, this is an  $O(n_1 \times n_2 \times \ldots \times n_{d-1})$  operation, which can be potentially expensive. These costs can be avoided for Array package Arrays, as the shapes of these Arrays are invariant during their lifetime.

#### 4 Experimental Results

We performed a series of experiments to measure the impact of the Array package and our compiler optimizations on the performance of Java numerical codes. In this section we present a summary of results for four benchmarks. We performed all our experiments on an IBM RS/6000 model 590 workstation. This machine has a 67 MHz POWER2 processor with a 256 kB single-level data cache and 512 MB of main memory. Its peak computational speed is 266 Mflops.

We compare the performance of three different versions of each benchmark. The first version is implemented in Fortran and serves as a performance reference. The second version is implemented in Java using only Java arrays. The third version is also implemented in Java, but using the Array package. Fortran programs are compiled using version 6.1 of the IBM XLF compiler with the highest level of optimization (-O3 -qhot, which performs high-order loop transformations [27]). For the Java arrays version, we report performance obtained using JDK 1.1.8 with the IBM JIT, which delivers the best performance for this version from all the Java environments available for our platform, including HPCJ. (The IBM JIT incorporates many advanced optimizations such as bounds checking and null-pointer checking optimization.) For the Array package version, we report the performance using our HPCJ-based compiler.

The benchmarks: The four benchmarks used are: MATMUL, BSOM, MICRO DC, and TOMCATV. MATMUL computes  $C=C+A\times B$ , where C,A, and B are matrices of size  $500\times 500$ . We use a dot-product version of matrix multiplication, with an This benchmark does not use the BLAS routines in the Array package. BSOM (Batch Self-Organizing Map) benchmark is a data-mining kernel. We time the execution of the training phase of this algorithm, which consists of 25 epochs. Each epoch updates a neural network with 16 nodes using 256 records of 256 fields each. MICRO DC solves the equation  $\nabla^2 \Phi = -\frac{\rho}{\epsilon}$  on a discretized domain using Jacobi relaxation [24]. For this benchmark, we use the problem configuration described in [21], with a  $1000\times 1000$  grid and four parallel microstrips of cross section  $100\times 10$  each. TOMCATV is part of the SPECfp95 suite (www.spec.org). For our experiments, we use a problem size n=513.

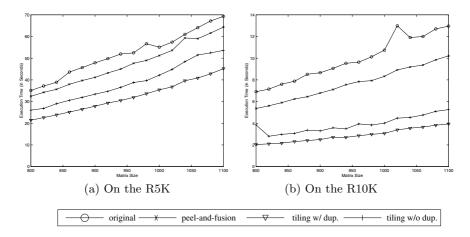

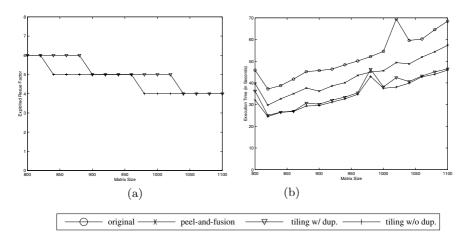

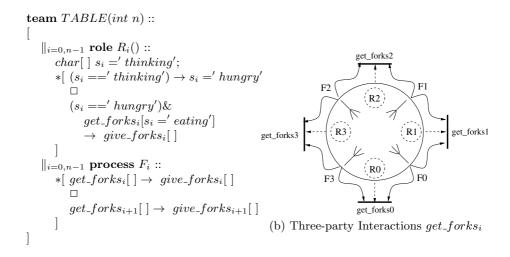

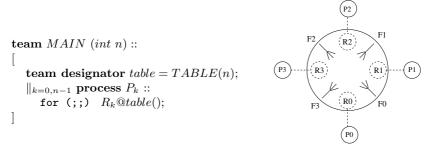

Results: Results for the four benchmarks are summarized in Table 1 and Figure 6. Table 1 summarizes the efficacy of our bounds checking optimization. For each benchmark, column "loops" lists the total number of loop constructs in the program. (The nest of Figure 5(a) counts as three loops.) Column "optimized" lists the number of loop constructs that can be optimized with our compiler. That is, the number of loops for which the compiler was able to compute complete array range information. Column

"coverage" is the ratio, in percentage, of loops optimized to total loops. Finally, column "safe regions" list the actual number of safe regions created for the benchmark. Since safe regions are created per loop nest, the number of safe regions can be much less than the number of optimized loops. For example, the safe region of Figure 5(b) optimizes three loops.

| benchmark | loops | optimized | coverage | safe regions |

|-----------|-------|-----------|----------|--------------|

| MATMUL    | 17    | 14        | 82.4%    | 6            |

| BSOM      | 25    | 21        | 84.0%    | 13           |

| MICRO DC  | 12    | 11        | 91.7%    | 5            |

| TOMCATV   | 20    | 20        | 100.0%   | 5            |

**Table 1.** Summary of loops optimized in each benchmark.

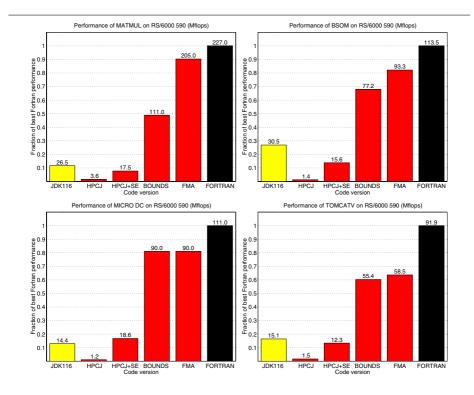

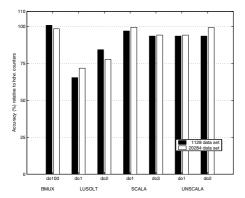

In the plots of Figure 6, the height of each bar is normalized with respect to the performance of the Fortran version. The numbers on the top of the bars indicate actual Mflops achieved for that version. The JDK118 bar shows the result for the Java array version, with JDK 1.1.8 + JIT. The HPCJ bar shows the result for the Array package version, as compiled by plain HPCJ (*i.e.*, with neither the semantic expansion nor bounds checking optimization). The HPCJ+SE bar shows the result for the Array package version with semantic expansion. The BOUNDS bar shows the best result that can be accomplished with 100% pure Java: it uses the Array package with semantic expansion and bounds checking optimization. The FMA bar shows the extra boost in performance that we can get by allowing Java to use the fused-multiply add (fma) instruction of the POWER architecture. Finally, the FORTRAN bar shows the result for the Fortran version of the benchmark. The Fortran version uses the fma instruction. (For the purpose of completeness, we report here that JDK 1.1.6 + JIT achieves 3.2, 1.7, 1.3, and 1.4 Mflops, or approximately the same as HPCJ, for the Array package versions of MATMUL, BSOM, MICRO DC, and TOMCATV, respectively.)

Discussion: The performance of numerical codes using Java arrays (the JDK116 bars) is clearly unsatisfactory. It is typically between 10% (MATMUL,MICRO DC) and 25% (BSOM) of Fortran performance. The performance of Array package code is terrible with standard Java environments (the HPCJ bars). The execution cost in this case is dominated by the overhead of method invocation. Even when semantic expansion is used (the HPCJ+SE bars), the performance of the Array package versions are almost always worse than the performance with Java arrays. Although semantic expansion eliminates the method overhead, the explicit bounds and null-pointer checks are expensive and prevent optimizations. It is only when bounds checking (and null-pointer checking) optimization is performed (the BOUNDS bars) that we start to see Java performance that is much better than with Java arrays and comparable with Fortran. Speedups over Java arrays vary from 2.5 (BSOM) to 6.3 (MICRO DC). Performance with semantic expansion and bounds optimization is between 50% (MATMUL) and 80% (MICRO DC) of Fortran. When fmas are allowed, the performance can be as high as 90% (MATMUL)

Fig. 6. Experimental results for all benchmarks.

of Fortran. We note that for three benchmarks (MATMUL, BSOM, and TOMCATV), fmas were generated by the compiler when enabled. The benefits of fmas are substantial for MATMUL and BSOM, less so for TOMCATV. For MICRO DC, no fmas were generated by the compilers (not even by the Fortran compiler).

#### 5 Related Work

The importance of having high-performance libraries for numerical computing in Java has been recognized by many authors. In particular, [5,6,28] describe projects to develop such libraries entirely in Java. In addition, there are approaches in which access to existing numerical libraries (typically coded in C and Fortran) is provided to Java applications [4, 8,14]. All of these approaches shift the burden of delivering high performance entirely to the libraries. It is well know that programming with libraries has its limitations. For this reason, the Array package is more than just a library: It is a mechanism to represent array operations in a manner that can be highly optimized by compilers.

In [10], Cierniak and Li describe a global analysis technique for determining that the shape of a Java array of arrays (e.g., double[][]) is indeed rectangular and not modified. The array representation is then transformed to a dense storage and element

access is performed through index arithmetic. This approach can lead to results that are as good as from using multidimensional Arrays in the Array package. We differ in that we do not need global analysis: Arrays from the Array package are intrinsically rectangular and can always be stored in a dense form.

The technique of semantic expansion we use is similar to the approach taken by Fortran compilers in implementing some *intrinsic* procedures [2]. Intrinsic procedures can be treated by the Fortran compiler as language primitives, just as we treated the get and set methods in various classes of the Array package. Semantic expansion differs from the handling of intrinsics in Fortran in that both new data types and operations on the new data types are treated as language primitives.

Marmot [12] is an optimizing static Java compiler being developed at Microsoft Research. It implements both standard scalar (Fortran and C style) optimizations and basic object oriented optimizations. It also performs bounds checking optimization by determining, through a form of range analysis, which checks are redundant. There is no discussion of versioning in [12]. Marmot shows significant speedups relative to other Java environments in several benchmarks, but its performance is only average for the numerical benchmarks listed in [12].

#### 6 Conclusion

We have demonstrated that high-performance numerical codes can be developed in Java. The benefits of Java from a productivity and demographics point of view have been known for a while. Many people have advocated the development of large, computationally intensive applications in Java based on those benefits. However, Java performance has consistently been considered an impediment to its applicability to numerical codes. This paper has presented a set of techniques that lead to Java performance that is comparable with the best Fortran implementations available today.

Adopting a language and compiler codesign approach, we have used a class library to introduce in Java features of Fortran 90 that are of great importance to numerical computing. These features include complex numbers, multidimensional arrays, and libraries for linear algebra. These features have a strong synergy with the compiler optimizations that we are developing, particularly bounds checking optimization and semantic expansion. All components of the Array package, including the BLAS library, are implemented entirely in Java. This guarantees portability of code and reproducibility of results in various platforms.

We demonstrated that we can deliver Java performance in the 65-90% range of the best Fortran performance for a variety of benchmarks. This is a very important step in making Java the preferred environment for developing large-scale computationally intensive applications. However, there is more than just performance to our approach. The Array package and associated libraries create a Java environment with many of the features that experienced Fortran programmers have grown accustomed to. This combination of delivering Fortran array manipulation features and performance, while maintaining the safety and elegance of Java, is the core of our approach to making Java the environment of choice for new numerical computing.

**Acknowledgements.** The authors wish to thank Rick Lawrence and Marc Snir for fruitful technical discussions, and for strongly supporting our research. We also wish to thank the members of the HPCJ and TPO teams at the IBM Toronto Lab for their work on the compiler infrastructure.

#### References

- Java Grande Forum report: Making Java work for high-end computing. Java Grande Forum Panel, SC98, Orlando, FL, November 1998. URL: http://www.javagrande.org/reports.htm.

- J. C. Adams, W. S. Brainerd, J. T. Martin, B. T. Smith, and J. L. Wagener. Fortran 90

Handbook: Complete ANSI/ISO Reference. McGraw-Hill, 1992.

- 3. Utpal Banerjee. *Dependence Analysis*. Loop Transformations for Restructuring Compilers. Kluwer Academic Publishers, Boston, MA, 1997.

- 4. A. Bik and D. B. Gannon. A note on level 1 BLAS in Java. In Proceedings of the Workshop on Java for Computational Science and Engineering - Simulation and Modeling II, June 1997. URL http://www.npac.syr.edu/users/gcf/03/javaforcse/ acmspecissue/latestpapers.html.

- B. Blount and S. Chatterjee. An evaluation of Java for numerical computing. In *Proceedings* of *ISCOPE'98*, volume 1505 of *Lecture Notes in Computer Science*, pages 35–46. Springer Verlag, 1998.

- R. F. Boisvert, J. J. Dongarra, R. Pozo, K. A. Remington, and G. W. Stewart. Developing numerical libraries in Java. In ACM 1998 Workshop on Java for High-Performance Network Computing. ACM SIGPLAN, 1998. URL: http://www.cs.ucsb.edu/conferences/java98.

- D. Callahan and K. Kennedy. Analysis of interprocedural side effects in a parallel programming environment. *Journal of Parallel and Distributed Computing*, 5:517–550, 1988.

- 8. H. Casanova, J. Dongarra, and D. M. Doolin. Java access to numerical libraries. *Concurrency, Pract. Exp. (UK)*, 9(11):1279–91, November 1997. Java for Computational Science and Engineering Simulation and Modeling II Las Vegas, NV, USA 21 June 1997.

- 9. M. Cierniak and W. Li. Unifying data and control transformations for distributed shared memory machines. In *Proc. ACM SIGPLAN '95 Conference on Programming Language Design and Implementation*, La Jolla, CA, June 1995.

- 10. M. Cierniak and W. Li. Just-in-time optimization for high-performance Java programs. *Concurrency, Pract. Exp. (UK)*, 9(11):1063–73, November 1997. Java for Computational Science and Engineering Simulation and Modeling II, Las Vegas, NV, June 21, 1997.

- 11. J. J. Dongarra, I. S. Duff, D. C. Sorensen, and H. A. van der Vorst. *Solving Linear Systems on Vector and Shared Memory Computers*. Society for Industrial and Applied Mathematics, 1991.

- 12. R. Fitzgerald, T. B. Knoblock, E. Ruf, Bjarne Steensgaard, and D. Tarditi. Marmot: an optimizing compiler for Java. Technical report, Microsoft Research, October 1998. URL: http://research.microsoft.com/apl/default.htm.

- 13. E. Gamma, R. Helm, R. Johnson, and J. Vlissides. *Design Patterns: Elements of Reusable Object-Oriented Software*. Addison-Wesley Publishing Company, 1995.

- V. Getov, S. Flynn-Hummel, and S. Mintchev. High-performance parallel programming in Java: Exploiting native libraries. In ACM 1998 Workshop on Java for High-Performance Network Computing. ACM SIGPLAN, 1998. URL: http://www.cs.ucsb.edu/ conferences/java98.

- M. Gupta, S. Mukhopadhyay, and N. Sinha. Automatic parallelization of recursive procedures. Technical Report RC 21333(96110)4NOV1998, IBM Research, November 1998.

- 16. F. G. Gustavson. Recursion leads to automatic variable blocking for dense linear algebra algorithms. *IBM Journal of Research and Development*, 41(6):737–755, November 1997.

- P. Havlak and K. Kennedy. An implementation of interprocedural bounded regular section analysis. *IEEE Transactions on Parallel and Distributed Systems*, 2(3):350–360, July 1991.

- 18. M. Kandemir, A. Choudhary, J. Ramanujam, and P. Banerjee. A matrix-based approach to the global locality optimization problem. In *Proceedings of International Conference on Parallel Architectures and Compilation Techniques (PACT'98), Paris, France*, October 1998.

- M. Kandemir, A. Choudhary, J. Ramanujam, N. Shenoy, and P. Banerjee. Enhancing spatial locality via data layout optimizations. In *Proceedings of Euro-Par'98, Southampton, UK*, volume 1470 of *Lecture Notes in Computer Science*, pages 422–434. Springer Verlag, September 1998.

- 20. S.P. Midkiff, J.E. Moreira, and M. Snir. Optimizing array reference checking in Java programs. *IBM Systems Journal*, 37(3):409–453, August 1998.

- 21. J. E. Moreira and S. P. Midkiff. Fortran 90 in CSE: A case study. *IEEE Computational Science & Engineering*, 5(2):39–49, April-June 1998.

- J. E. Moreira, S. P. Midkiff, and M. Gupta. From flop to Megaflops: Java for technical computing. In *Proceedings of the 11th International Workshop on Languages and Compilers* for Parallel Computing, LCPC'98, 1998. IBM Research Report 21166.

- 23. R. Parsons and D. Quinlan. Run time recognition of task parallelism within the P++ parallel array class library. In *Proceedings of the Scalable Parallel Libraries Conference*, pages 77–86. IEEE Comput. Soc. Press, October 1993.

- 24. W. H. Press, S. A. Teukolsky, W. T. Vetterling, and B. P. Flannery. *Numerical Recipes in FORTRAN: The Art of Scientific Computing*. Cambridge University Press, 1992.

- 25. J. V. W. Reynders, J. C. Cummings, M. Tholburn, P. J. Hinker, S. R. Atlas, S. Banerjee, M. Srikant, W. F. Humphrey, S. R. Karmesin, and K. Keahey. POOMA: A framework for scientific simulation on parallel architectures. In *Proceedings of First International Workshop on High Level Programming Models and Supportive Environments, Honolulu, HI*, pages 41–49, April 16 1996. URL: http://www.acl.lanl.gov/PoomaFramework/papers/papers.html.

- G. Rivera and C.-W. Tseng. Data transformations for eliminating conflict misses. In *Proceedings of the ACM SIGPLAN'98 Conference on Programming Language Design and Implementation*, pages 38–49, Montreal, Canada, June 1998. ACM Press.

- 27. V. Sarkar. Automatic selection of high-order transformations in the IBM XL Fortran compilers. *IBM Journal of Research and Development*, 41(3):233–264, May 1997.

- 28. M. Schwab and J. Schroeder. Algebraic Java classes for numerical optimization. In *ACM 1998 Workshop on Java for High-Performance Network Computing*. ACM SIGPLAN, 1998. URL: http://www.cs.ucsb.edu/conferences/java98.

- 29. G. V. Wilson and P. Lu, editors. *Parallel Programming using C++*. MIT Press, 1996.

- 30. P. Wu, S. P. Midkiff, J. E. Moreira, and M. Gupta. Efficient support for complex numbers in Java. In *Proceedings of the 1999 ACM Java Grande Conference*, 1999. IBM Research Division report RC21393.

# Instruction Scheduling in the Presence of Java's Runtime Exceptions

Matthew Arnold<sup>1</sup>, Michael Hsiao<sup>2</sup>, Ulrich Kremer<sup>1</sup>, and Barbara Ryder<sup>1</sup>

Department of Computer Science, Rutgers University, Piscataway NJ 08855, USA {marnold,uli,ryder}@cs.rutgers.edu,

http://www.prolangs.rutgers.edu

Department of Electrical and Computer Engineering, Rutgers University,

Piscataway NJ 08855, USA

mhsiao@ece.rutgers.edu

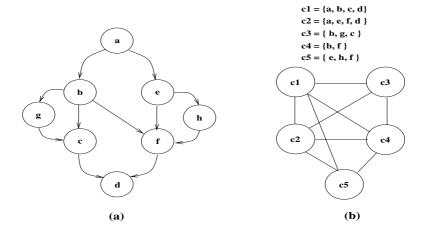

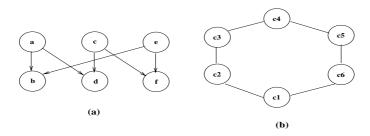

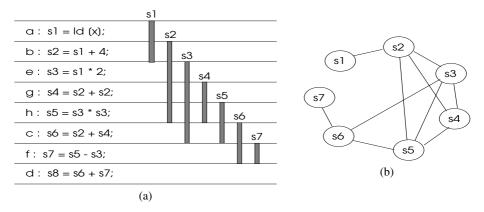

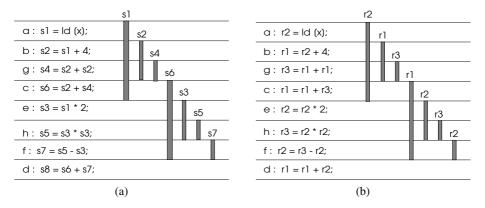

Abstract. One of the challenges present to a Java compiler is Java's frequent use of runtime exceptions. These exceptions affect performance directly by requiring explicit checks, as well as indirectly by restricting code movement in order to satisfy Java's precise exception model. Instruction scheduling is one transformation which is restricted by runtime exceptions since it relies heavily on reordering instructions to exploit maximum hardware performance. The goal of this study was to investigate the degree to which Java's runtime exceptions hinder instruction scheduling, and to find new techniques for allowing more efficient execution of Java programs containing runtime exceptions.

#### 1 Introduction

Java programs were originally executed by compiling Java source into bytecodes and interpreting these bytecodes on a Java Virtual Machine. Today, interpretation is being replaced by *Just In Time* (JIT) and dynamic compilers. As Java is becoming more popular as a general purpose programming language, the demand for a high performance native code Java compiler is increasing as well.

One of the challenges present to any Java compiler is Java's frequent use of exceptions. Several Java statements implicitly throw exceptions, including array accesses, pointer uses, casts, and integer division. These implicit exceptions, or runtime exceptions, directly affect performance by requiring the insertion of explicit runtime checks. Performance is also affected indirectly by Java's precise exception model which restricts code movement, making many optimizations and transformations more difficult.

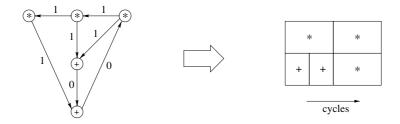

Instruction scheduling is one example of a compiler transformation which is affected by Java's runtime exceptions since it relies heavily on reordering instructions to exploit maximum hardware performance, particularly on advanced architectures such as superscaler and VLIW. The instruction reordering restrictions imposed by runtime exceptions can hinder the effectiveness of the instruction scheduler, and as a result, substantially reduce the amount of instruction level parallelism.

L. Carter and J. Ferrante (Eds.): LCPC'99, LNCS 1863, pp. 18-34, 2000.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2000

One approach to reduce the overhead introduced by runtime exceptions is to use static analysis to identify instructions which are known never to throw exceptions, allowing the runtime checks for these instructions to be safely removed. While this technique important, it may not be sufficient if many of the checks cannot be eliminated.

The goal of this study was to investigate the degree to which Java's runtime exceptions hinder instruction scheduling, and to find new techniques for allowing more efficient execution of Java programs containing runtime exceptions.

The contributions of this paper are as follows:

- We discuss the issues related to instruction scheduling in the presence of Java's runtime exceptions.

- We discuss existing techniques which can be used to improve performance without violating the Java exception model semantics.

- We offer experimental results showing the degree to which runtime exceptions hinder performance on both modern and future architectures. We also show results confirming that techniques such as superblock scheduling can be used to substantially reduce this penalty.

#### 1.1 Exceptions in Java

Java's precise exception model imposes restrictions on optimizations in the presence of exceptions. The exception model is defined in [8], section 11.3.1, as follows

Exceptions in Java are precise: when the transfer of control takes place, all effects of the statements executed and expressions evaluated before the point from which the exception is thrown must appear to have taken place. No expressions, statements, or parts thereof that occur after the point from which the exception is thrown may appear to have been evaluated. If optimized code has speculatively executed some of the expressions or statements which follow the point at which the exception occurs, such code must be prepared to hide this speculative execution from the user-visible state of the Java program.

Section 6 contains further discussion regarding interpreting the Java specification. For now, we will assume that meeting the following three restrictions is sufficient to satisfy the exception model described above, and we will show that our transformations satisfy these restrictions.

- 1. Exceptions occur in the same order in the optimized and unoptimized code, regardless of what optimizations are performed.

- 2. An exception is thrown if and only if it is thrown in the unoptimized program.

- 3. When an exception occurs, program execution following the point of the exception will observe the user visible state to be identical to what it would have been if no optimization had taken place.

The most obvious solution to maintain exception order is to add the explicit exception checks *before* any optimizations take place. As long as the compiler does not re-order the checks themselves, the exceptions will occur in the original order. The compiler must then speculate code in such a way that state is guaranteed to be correct if an exception occurs. The addition of runtime checks increases the number of jumps and reduces the size of the basic blocks, greatly hindering traditional instruction schedulers.

#### 2 Advanced Instruction Scheduling

The following is a review of existing instruction scheduling techniques which were designed for programs written in C. One of the primary goals of these techniques is to allow speculation of instructions while ensuring that hardware exceptions occur correctly. At this point we must make it clear that this work deals with hardware exceptions, not Java's runtime exceptions. To avoid confusion, for the rest of this paper exceptions will always be referred to as either hardware exceptions or Java exceptions. There are also two types of hardware exceptions – those which terminate the program execution, such as segmentation fault and bus errors, and those which do not, such as page faults, cache misses and TLB misses. These non-terminating exceptions will be referred to as transparent exceptions.

In later sections we will discuss how the techniques described below can be used to improve instruction scheduling for Java programs.

#### 2.1 Superblock Scheduling

Superblock scheduling [10] is an extension of trace scheduling [7]. The goal of superblock scheduling is to combine sets of basic blocks which are likely to execute in sequence, thus allowing more effective instruction scheduling. Flow of control may exit the superblock early along branches which are unlikely to be taken. Side entrances into the superblock are eliminated by using tail duplication.

To ensure proper program execution, two restrictions must be enforced when moving instructions within the superblock. An instruction, J, may be moved before a branch, BR if (1) the destination of J is not used before it is redefined when BR is taken, and (2) J will not cause a hardware exception which alters the execution result of the program when BR is taken.

Restricted Percolation The scheduler enforces both restrictions (1) and (2) when using the restricted percolation model. Only those instructions which are guaranteed not to cause a hardware exception can be speculatively executed; otherwise an incorrect, or *spurious exception* could occur.

General Percolation The scheduler completely ignores restriction (2) when using the general percolation model. This can be accomplished if the architecture supports non-excepting, or silent, instructions. When a terminating hardware exception occurs for a silent instruction, the exception is simply ignored and a garbage value is written into the destination register. This ensures that spurious exceptions will not affect program execution. If the exception is not spurious (i.e., it would have appeared in the original program) it will be ignored by general percolation and program execution will continue. This may lead to incorrect results, or a later exception being raised.

The obvious drawback of general percolation is the inability to detect hardware exceptions properly, making debugging and error detection very difficult. Failure to accurately detect hardware exceptions is unacceptable in many cases, and thus general percolation is used mostly as a best case scenario for other speculation models.

#### 2.2 Sentinel Scheduling

Sentinel scheduling [13] attempts to provide the scheduling freedom of general percolation while always detecting hardware exceptions and identifying the excepting instructions. The basic idea behind sentinel scheduling is that each potentially excepting instruction (PEI) has a sentinel which reports any exception that was caused by the PEI. The sentinel resides in the PEI's original basic block, or home block. If the home block is never reached then the exception is not raised, thus eliminating spurious exceptions.

If a sentinel for an excepting instruction is reached, the process of *recovery* is begins. Program execution jumps back to the speculatively executed instruction and it is re-executed non-speculatively, thus causing the exception to occur. If the exception is non-terminating then the exception is processed and program execution continues. The sequence of instructions between the PEI and the sentinel are re-executed thus the compiler must ensure that this sequence of instruction is always re-executable.

Sentinel scheduling requires architectural support, including an extra bit on all registers to record whether a speculative instruction caused an exception, as well an extra bit in the opcode to distinguish speculative and non-speculative instructions. It is worth noting that the IA-64 architecture [11] will provide this hardware support for speculative loads, making sentinel scheduling and general percolation possible.

One of the problems associated with sentinel scheduling is that maintaining this sequence of re-executable instructions significantly increases register pressure. Techniques such as [4][3] were presented in an attempt to solve this problem and thus decrease the performance difference between sentinel scheduling and general percolation.

## 3 Combining Advanced Scheduling and Java

Superblock scheduling is very effective for code consisting of small basic blocks in combination with predictable branches; this is exactly the type of code that is created when runtime exception checks are added to a Java program. We propose that the following algorithm is effective for reducing the performance penalty of Java's runtime exceptions.

#### Algorithm 1

x = A[i];

- 1. **Remove unnecessary checks.** If it can be determined at compile time that an exception can not occur, that exception check can be removed. Removing as many checks as possible eliminates the overhead of the checks and relaxes restrictions on code movement.

- 2. Make all remaining exception checks explicit. For example, the code:

x = A[i]; becomes:

- if (A == null) throw new NullPointerException();

if (OUT\_OF\_BOUND(A,i))throw new ArrayIndexOutOfBoundException();

- 3. Form superblocks. Form superblocks and schedule using general percolation as the speculation model.

Notice that general percolation is used as the speculation model in step 3, therefore requiring the architectural support discussed in Section 2. By using general percolation, instructions may be speculated without concern for hardware exceptions. The result is that hardware exceptions may go undetected, but as long as these exceptions would not have occurred in the original code, the program is guaranteed to execute properly (as if no speculation had occurred). For now it should be assumed that the original program does not raise terminating hardware exceptions and thus the use of general percolation is acceptable. This issue is discussed in detail in section 5.1.

Superblock scheduling is particularly effective for code containing exceptions because it takes advantage of the fact that exceptions rarely occur. Each exception check becomes a branch exiting the superblock. By using general percolation, the compiler is given more leeway to speculate instructions within the superblock.

As for any Java transformation, the compiler must ensure that the Java exception model is not violated. As discussed in section 1.1, the following 3 properties are satisfied.

- 1. Java exception order is preserved. The key to maintaining exception order is the fact that each potentially excepting instruction is guarded by an explicit exception check. Instructions such as array accesses may be speculated; however, since the bounds checks are executed in the original order, Java exceptions are guaranteed to occur in the same order.

- 2. Java exceptions occur if and only if they occur in the original program. Again, the Java exception checks were made explicit, so assuming that the superblock scheduler maintains the semantics of the original program, Java exceptions will occur as they did in the original program.

<sup>&</sup>lt;sup>1</sup> Some exceptions can be checked implicitly by looking for the hardware exception that occurs when the instruction is executed. This technique can be used, but requires a more intelligent scheduler. This issue is discussed in Section 5.3 in detail.

3. State is maintained when a Java exception occurs. Recall restriction (1) from section 2. Even in general percolation, an instruction, J, is not speculated above a branch if J's destination register is used before defined when the branch is taken. Thus when a Java exception occurs, all variables and registers which are used during and after the handling of the exception will be the same as if superblock scheduling had not taken place.

#### 4 Experimental Results

To measure the performance impact of Java's runtime exceptions we modified Toba [15], a Java to C converter, so that the insertion of runtime exception checks could be turned on and off. Since the Java exceptions will not be detected when the checks are not inserted, this experimental technique works only for programs which do not throw runtime exceptions. The resulting C programs were then compiled using the Trimaran [1] system, a framework designed for research in instruction level parallelism. The Trimaran compiler performs many optimizations and transformations, including superblock scheduling, and allows the code to be simulated on a parameterized processor architecture called HPL-PD.

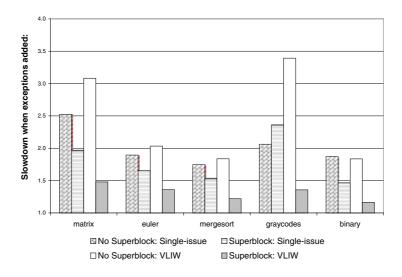

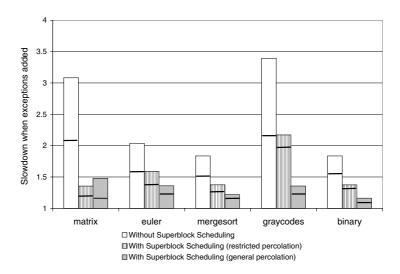

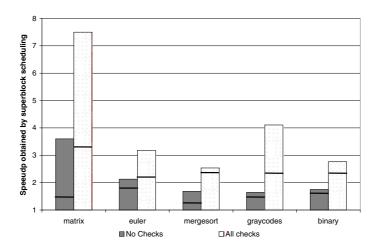

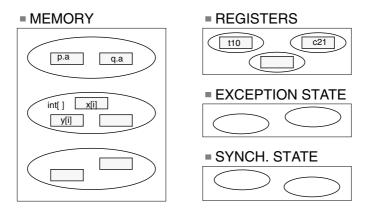

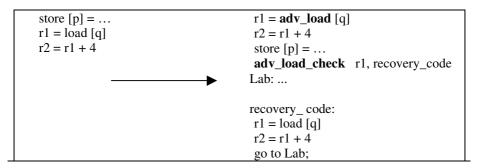

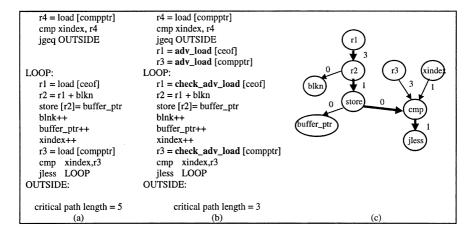

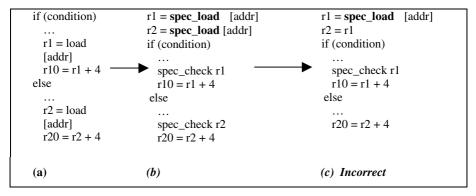

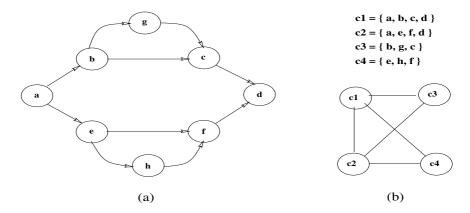

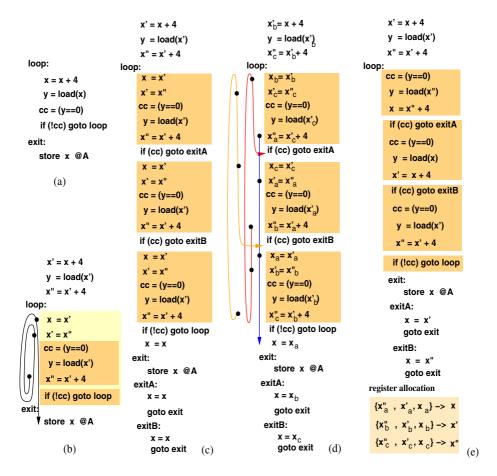

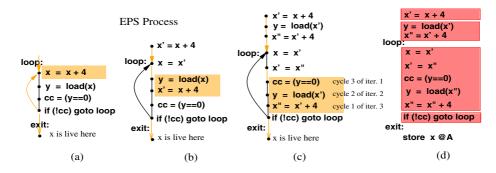

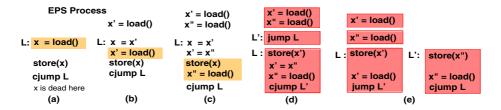

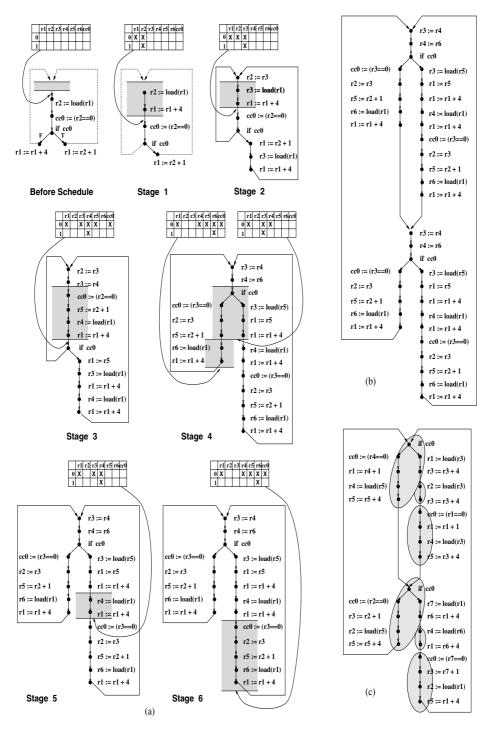

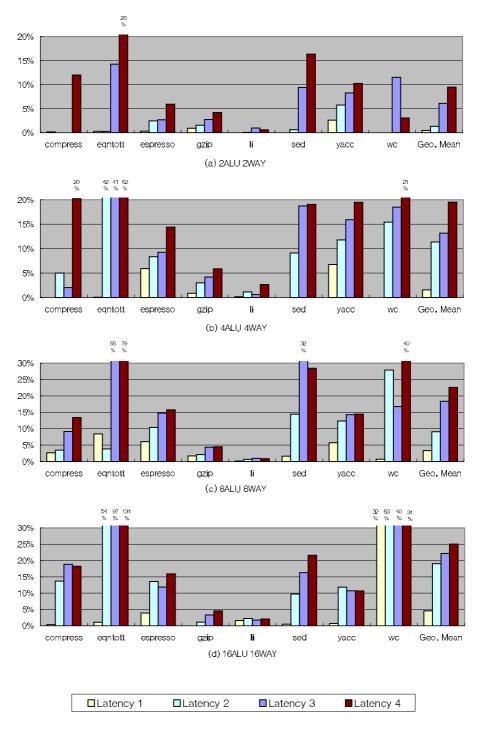

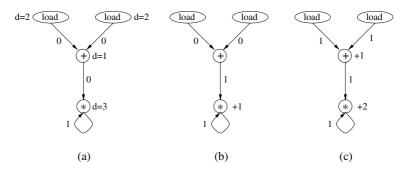

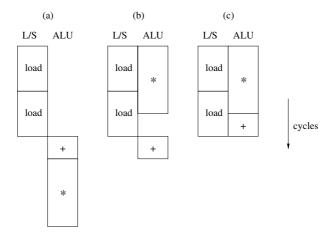

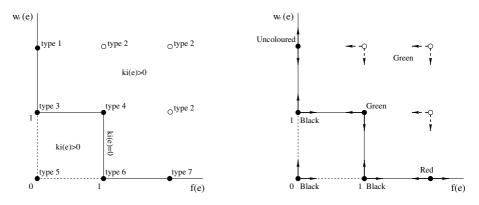

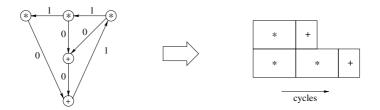

The C programs produced by Toba were compiled with and without superblock scheduling, and simulated on two of the sample machines provided in the Trimaran release. Both machines were specified using MDES, Trimaran's machine description language. The first machine, a VLIW machine capable of issuing 9 instructions per cycle, contains 4 integer units, 2 floating point units, 2 memory units, and 1 branch unit. The second machine, which will be referred to as the *single-issue* machine, is capable of issuing only one instruction per cycle and has one of each functional unit mentioned above. Each machine has 64 general purpose registers.